Tanmay's Design Study

Tanmay Bhola (Talk | contribs) |

Tanmay Bhola (Talk | contribs) |

||

| Line 33: | Line 33: | ||

[[Image:Tbh_Final_Design.png]] | [[Image:Tbh_Final_Design.png]] | ||

| − | == Design Detail | + | == Design Detail == |

'''Modelling Components using the Composite Pattern''' | '''Modelling Components using the Composite Pattern''' | ||

| Line 44: | Line 44: | ||

A wire is essentially a link between two components, and carries (holds) a '1/0' value at any time. The outputs of components SET the value of the view while this change in the value triggers events in components via their inputs. The Observer pattern might be helpful in notifying a subset of components in the circuit (observers !!! ) when the value of the wire changes. Hence the components also implement the <<observer>> interface and can subscribe to changes in the status of the wires connected at their inputs. On receiving such changes, they can recalculate the output values (using the function they implement) and update the output wire status. | A wire is essentially a link between two components, and carries (holds) a '1/0' value at any time. The outputs of components SET the value of the view while this change in the value triggers events in components via their inputs. The Observer pattern might be helpful in notifying a subset of components in the circuit (observers !!! ) when the value of the wire changes. Hence the components also implement the <<observer>> interface and can subscribe to changes in the status of the wires connected at their inputs. On receiving such changes, they can recalculate the output values (using the function they implement) and update the output wire status. | ||

| − | == | + | == Patterns and Principles == |

| − | == Design Critique == | + | == Discussion and Design Critique == |

| − | === | + | 1) The Composite Design Pattern: No-Op Overrides Vs Dependency Inversion Principle |

| + | |||

| + | 2) Push Vs. Pull Configuration of the Observer | ||

| + | |||

| + | == Extensibility of Design == | ||

| + | |||

| + | == Conclusion == | ||

Revision as of 23:26, 29 September 2010

Contents |

Introduction

Welcome to the world of Digital Logic. Ever wondered what they teach at the College of Engineering that is different from the material taught at Department of Computer Science and Software Engineering ? Being a computer engineering student, I thought I would take this opportunity to perform Object-Oriented Analysis and Design of a 'Digital Logic Circuit Simulator'. Digital Circuits are constructed by joining simple logic elements and form the basis of the 'Embedded Systems' oriented programme.

Background

Building complex digital structures like computers and microcontrollers without a simulation tool is similar to releasing a program without compiling/testing. Hence, designers always resort to simulation tools to check the correctness of their design before building the prototype. These circuits are essentially complex networks of simple logic components like logic gates, wires, clocks etc.

A digital logic simulator gives the user an ability to join simple logic elements in order to study the behaviour of complex digital circuits. My approach to this problem was to design an 'Event Driven Simulator' where events (change in state of something) trigger further events in the system at a later time. The main tasks revolved around the elementary components of the circuit and scheduling events that take place in the system. These can be further broken down into :

- 1) Wires --- Carry digital logic signals between components

- 2) Digital Function Blocks --- Perform functions to generate output signal(s) based on some inputs. They need to listen for changes in the state of wires connected to these blocks.

- 3) Events --- to help model the time delay of performing various tasks during the simulation. A change in the state of 1 wire might trickle down to changes in the neighboring wires based on the output of the connecting function blocks.

My primary focus for this design study was on modelling the core classes of the simulator rather than its GUI implementation.

Requirements

- 1) Adding Components : A User should be able to add new components to the system. These components can be a basic logic element or a combination of a series of elements. The user should also be able to copy simple elements in order to quickly build up a circuit. This is useful as many basic elements like logic gates are repeated in the circuit.

- 2) Connecting Components with Wires : A user should be able to assign connecting wires to the component input/ output ports. On connection, the component should be ready to respond to changes in the state of the wire.

- 3) Running the Simulation : Once the circuit has been wired up, a user should be able to run the simulation and view the results via a component like a probe.

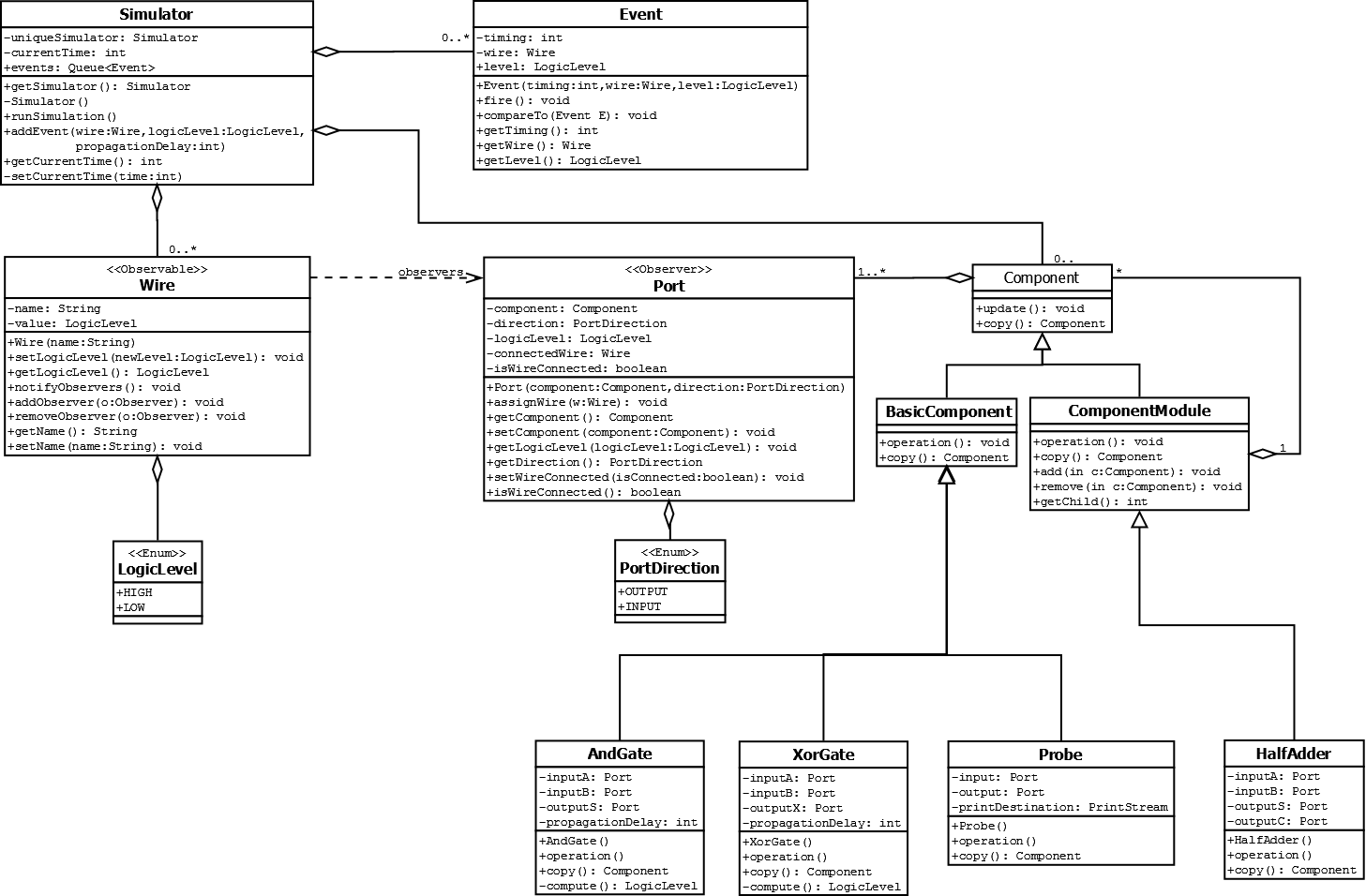

UML Diagram Of Design

Design Detail

Modelling Components using the Composite Pattern

Components could be in the form of simple logic gates (and/or/xor etc.) or a combination of these forming more complex components. The first pattern that comes to mind when thinking about part-whole hierarchies is the Composite Pattern. Hence, this pattern will be used for modelling the components as a start. A high level interface would be used to hide the complexity of individual components and encourage programming to the interface, not the implementation.

Lower level components should be able to take in Wires as their inputs and outputs to help with wiring up the circuit.

Modelling a Wire

A wire is essentially a link between two components, and carries (holds) a '1/0' value at any time. The outputs of components SET the value of the view while this change in the value triggers events in components via their inputs. The Observer pattern might be helpful in notifying a subset of components in the circuit (observers !!! ) when the value of the wire changes. Hence the components also implement the <<observer>> interface and can subscribe to changes in the status of the wires connected at their inputs. On receiving such changes, they can recalculate the output values (using the function they implement) and update the output wire status.

Patterns and Principles

Discussion and Design Critique

1) The Composite Design Pattern: No-Op Overrides Vs Dependency Inversion Principle

2) Push Vs. Pull Configuration of the Observer